- 您现在的位置:买卖IC网 > Sheet目录2007 > M-986-2A1PL (IXYS Integrated Circuits Division)IC TRANSCEIVER MF 2CHAN 44-PLCC

www.clare.com

6

M-986-2A1

Rev. 3

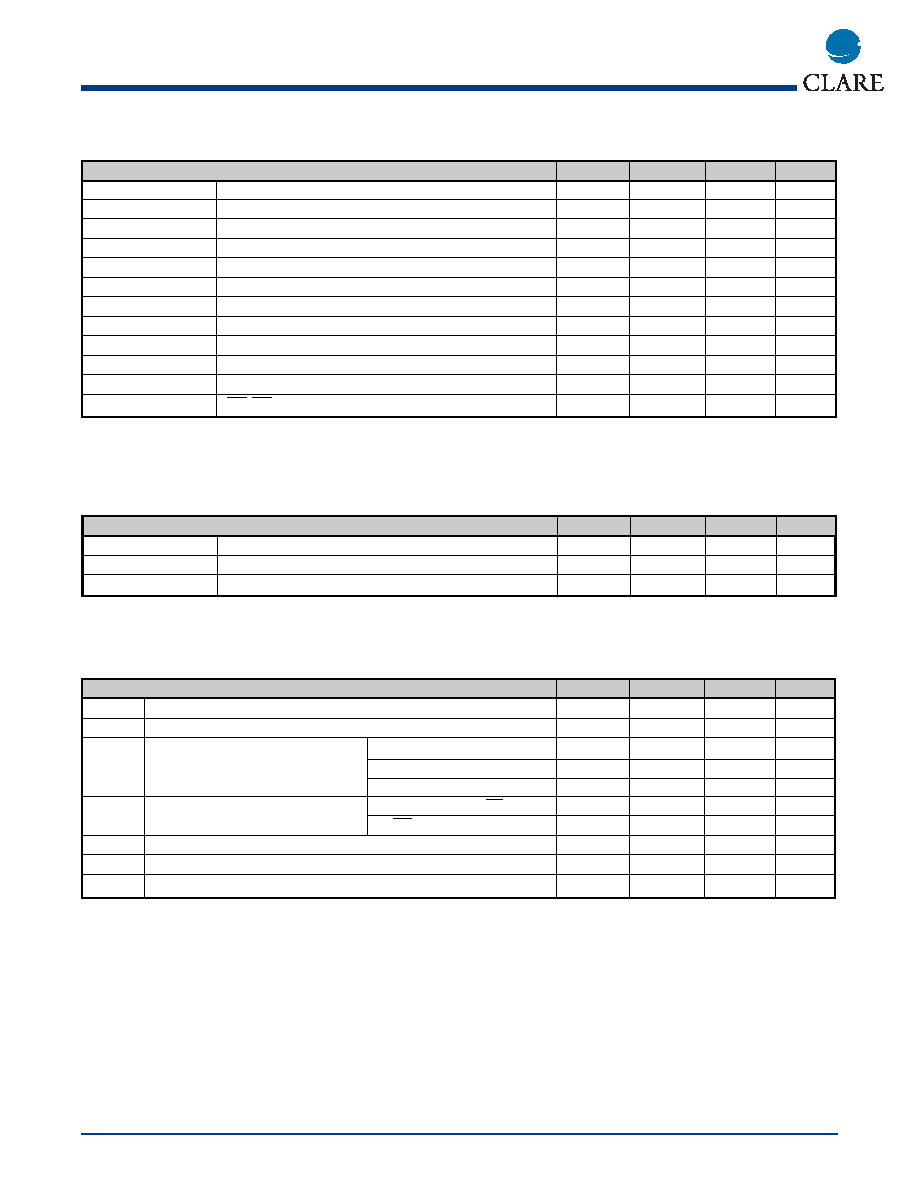

Serial Port Timing

Parameter

Min

Nom

Max

Unit

t

d (CH-FR)

Internal framing delay from SCLK rising edge

-

70

ns

t

d (DX1-CL)

DX bit 1 valid before SCLK falling edge

20

-

ns

t

d (DX2-CL)

DX bit 2 valid before SCLK falling edge

20

-

ns

t

h (DX)

DX hold time after SCLK falling edge

244

-

ns

t

su (DR)

DR setup time before SCLK falling edge

20

-

ns

t

h (DR)

DR hold time after SCLK falling edge

20

-

ns

t

c (SCLK)

Serial port clock cycle time

399

488.28

4770

ns

t

f (SCLK)

Serial port clock fall time

-

30

ns

t

r (SCLK)

Serial port clock rise time

-

30

ns

t

w (SCLKL)

Serial port clock low-pulse duration*

220

244.14

2500

ns

t

w (SCLKH)

Serial port clock high-pulse duration*

220

244.14

2500

ns

t

su (FS)

FSX/FSR setup time before SCLK falling edge

100

-

ns

* The duty cycle of the serial port clock must be within 45% to 55%.

External Frequency Specifications

Parameter

Min

Nom

Max

Unit

t

C(MC)

Master clock cycle time

48.818

48.828

48.838

ns

t

r(MC)

Rise time master clock input

-

5

10

ns

t

f(MC)

Pulse duration master clock

20

-

ns

Recommended Operating Conditions

Parameter

Min

Nom

Max

Unit

V

CC

Supply voltage

4.75

5

5.25

V

SS

Supply voltage

-

0

-

V

IH

High-level input voltage

All inputs except CLKIN

2

-

V

CLKIN

3

-

V

MC/PM

2.2

-

V

IL

Low-level input voltage

All inputs except MC/MP

-

0.8

V

MC/MP

-

0.6

V

I

OH

High-level output current (all outputs)

-

-300

A

I

OL

Low-level output current (all outputs)

-

2

mA

T

A

Operating free-air temperature

0

-

70

C

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX038CWP+

IC GEN WAVEFORM HI-FREQ 20-SOIC

MAX1002CAX+T

IC ADC 6BIT 60MSPS DUAL 36-SSOP

MAX1003CAX

IC ADC DUAL 6-BIT 90MSPS 36-SSOP

MAX1011CEG+

IC ADC 6BIT 90MSPS 24-QSOP

MAX105ECS+T

IC ADC 6BIT 800MSPS DL 80TQFP

MAX1063AEEG+

IC ADC 10BIT 250KSPS 24-QSOP

MAX107ECS+

IC ADC 6BIT 400MSPS DL 80-TQFP

MAX1080AEUP+

IC ADC 10BIT 400KSPS 20-TSSOP

相关代理商/技术参数

M-986-2R2

制造商:CLARE 制造商全称:Clare, Inc. 功能描述:MFC Transceivers

M-986-2R2P

功能描述:固态继电器-PCB安装 MF Transceiver, dual channel, 40xpin RoHS:否 制造商:Omron Electronics 控制电压范围: 负载电压额定值:40 V 负载电流额定值:120 mA 触点形式:1 Form A (SPST-NO) 输出设备:MOSFET 封装 / 箱体:USOP-4 安装风格:SMD/SMT

M-986-2R2PL

功能描述:固态继电器-PCB安装 MF Transceiver, dual channel, 44xpin RoHS:否 制造商:Omron Electronics 控制电压范围: 负载电压额定值:40 V 负载电流额定值:120 mA 触点形式:1 Form A (SPST-NO) 输出设备:MOSFET 封装 / 箱体:USOP-4 安装风格:SMD/SMT

M9866

制造商:Tamura Corporation of America 功能描述:

M9870

制造商:Tamura Corporation of America 功能描述:

M-987-2A1K

功能描述:IC TRANSCEIVER MF 2CH 144-TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 电信 系列:* 产品培训模块:Lead (SnPb) Finish for COTS 产品变化通告:Product Discontinuation 06/Feb/2012 标准包装:750 系列:*

M-987-2A1KTR

功能描述:IC TRANSCEIVER MF 2CH 144-TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 电信 系列:* 产品培训模块:Lead (SnPb) Finish for COTS 产品变化通告:Product Discontinuation 06/Feb/2012 标准包装:750 系列:*

M9874

制造商:Tamura Corporation of America 功能描述: